## Status of the Development of On-Detector Array-based Optical Link

A. Adair, W. Fernando, K.K. Gan, H.P. Kagan, R.D. Kass,H. Merritt, J. Moore, A. Nagarkar, S. Smith, M. Strang The Ohio State University

> P. Buchholz, A. Wiese, M. Ziolkowski Universität Siegen

> > T. Flick, P. Maettig Universität Wuppertal

A. Pellegrino, T. Sluijk NIKHEF (LHCb)

March 5, 2010

Joint ATLAS/CMS SLHC Opto WG

## Outline

- Introduction

- Current work with IBL

- Schedule

## IBL

ATLAS proposed to add one more layer to the current pixel detector:

- "Inner B-Layer" or IBL

- to be installed ~ 2014

- optical links will use VCSEL/PIN array as in current pixel detector

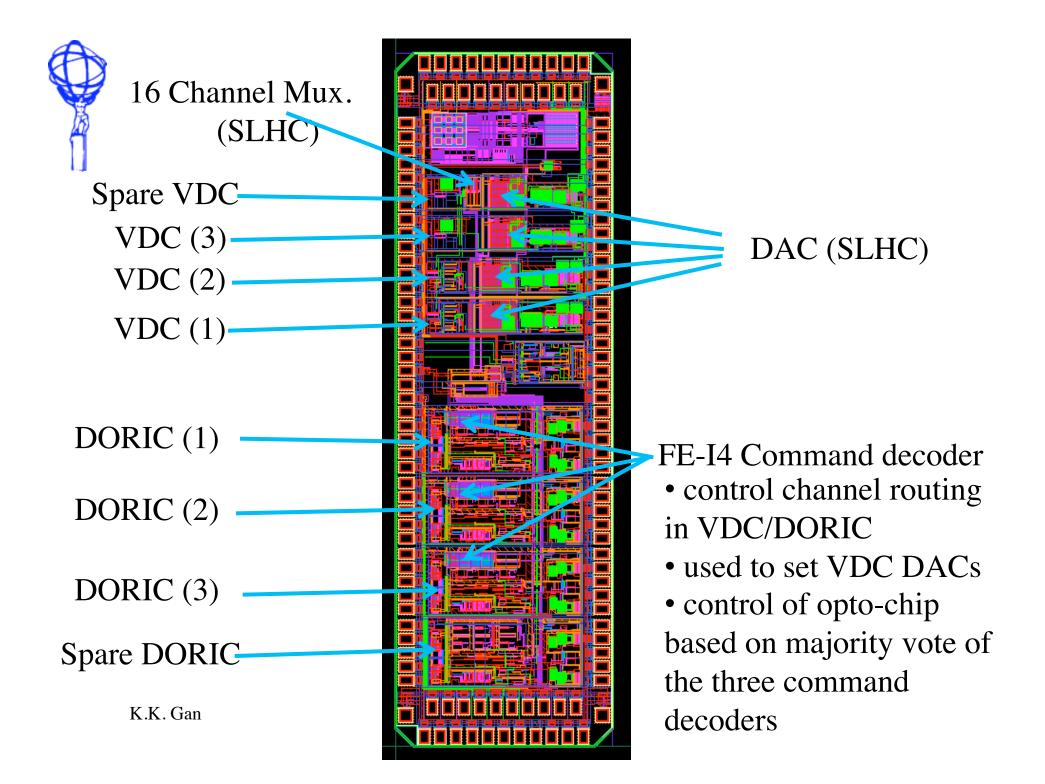

- an updated version of current driver (VDC) and receiver (DORIC) with redundancy and individual VCSEL current control would be a logical improvement

- experience gained from the development/testing of such new chips would help the development of on-detector array-based opto-links for SLHC

- $\Rightarrow$  submission of 1<sup>st</sup> IBL prototype chip (130 nm) in 2/2010

Power on reset circuit

Opto-Chip Control Logic

• Interfaces opto-chip controls to the 3 FE-I4 command decoders

- Contains SEU tolerant DICE latches from FE-I4

- Power on reset circuit to set default VCSEL current to 10 mA

## Schedule

- The proposed schedule called for SLHC array chip submission in 11/2010 (4 channels) and 12/2011 (12 channels), followed by irradiation of chips from each submission.

- There is no urgency to submit in 11/2010

- chip should be submitted when a design has been thoroughly simulated

- all are invited to join the effort!