#### Opto-Packs for On-Detector Pixel Opto-Links

B. Cote, K.K. Gan, H. Kagan, Z. Pollock, S. Smith, C. Tandoi, B. Tar, A. Woyshville The Ohio State University

> P. Buchholz, M. Ziolkowski Universität Siegen

> > June 3, 2019

Pixel Opto Review

#### Outline

- Opto-pack design

- Production experience

- Summary

## History of Pixel Opto-Packs

- <sup>1</sup><sup>st</sup> generation opto-boards used opto-packs produced by Taiwan

- clever design but difficult to connect

- 0.1% of optical links built by Ohio State failed

- used Truelight VCSEL/PIN arrays

- $\Rightarrow$  new opto-pack design used in 2<sup>nd</sup> generation opto-boards

- 2% of optical links failed

- used Finisar VCSEL and ULM PIN arrays

- no indication that problem is due to opto-packs

- $\Rightarrow$  propose to continue to use 2<sup>nd</sup> generation opto-pack

- some of data shown are from 2013/14 production

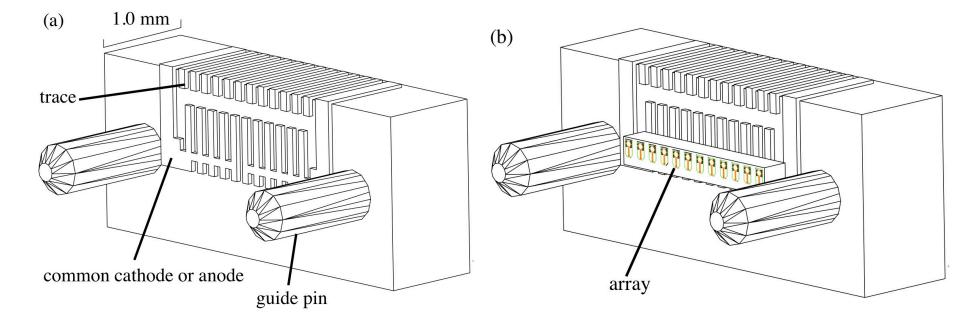

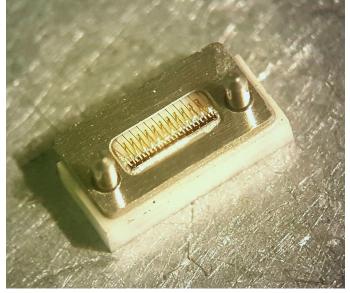

### Design of 2<sup>nd</sup> Generation Opto-Pack

- Use BeO as substrate for heat management

- Use wire bonds to connect to opto-board

- Final system needs 600 VCSEL and 300 PIN opto-packs

#### Production Procedure

- Glue guide pins to BeO with precise location defined by MT ferrule

- Cure the epoxy

- Insertion force test to ensure two guide pins are parallel

- Deposit conducting epoxy on BeO

- Place VCSEL or PIN array on BeO

- Align the array

- Cure the epoxy

- Wire bond the array

- Attach shield to prevent wire bonds being crashed by MT ferrule

- Add Kapton tape to seal off opening to prevent dust from entering

all steps (exclude epoxy curing) is ~2 hours

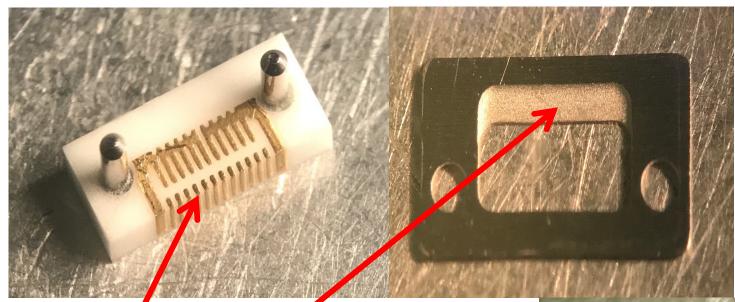

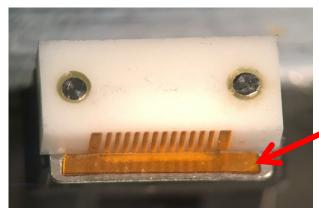

#### **Opto-Pack**

Indentation to prevent shorting of traces

Opening covered with Kapton tape

K.K. Gan

## **CSEL Opto-pack Production Experience**

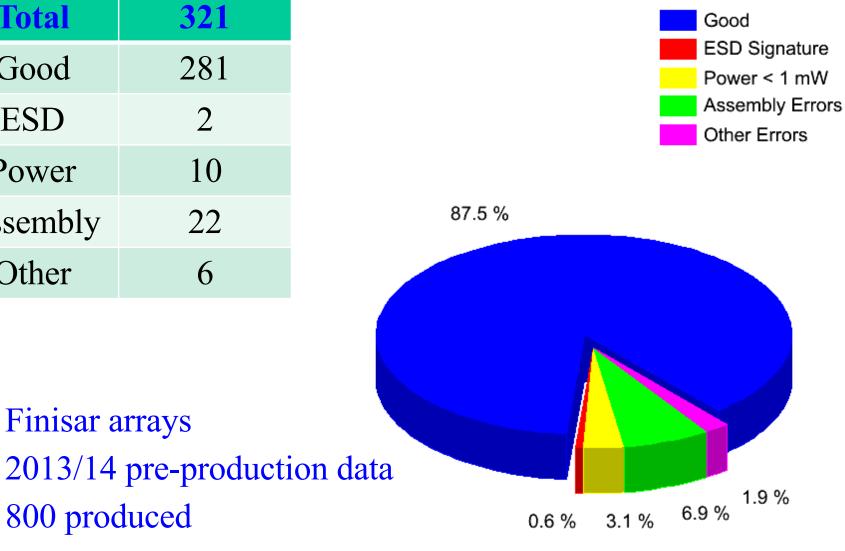

| Total    | 321 |

|----------|-----|

| Good     | 281 |

| ESD      | 2   |

| Power    | 10  |

| Assembly | 22  |

| Other    | 6   |

K.K. Gan

**Finisar arrays**

800 produced

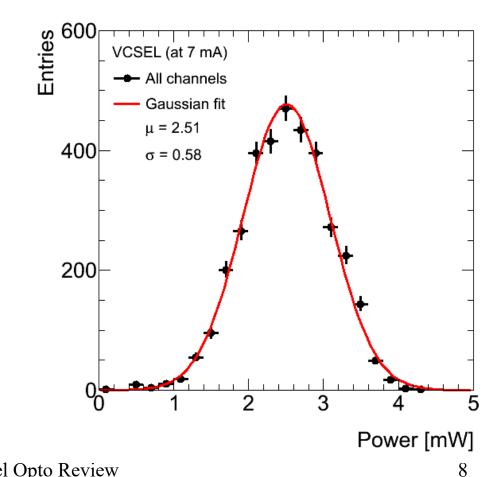

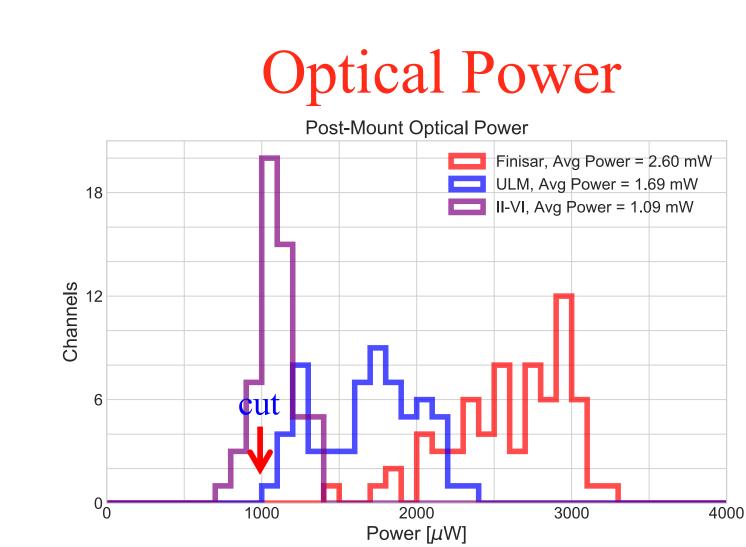

#### **VCSEL** Optical Power

- average optical power ~2.5 mW

- require 1 mW @ 7 mA in QA (max current 11 mA)

- shield with thickness of 254 μm was designed for Finisar array with thickness of 200 μm

- ULM/II-VI array thickness is 150 µm

⇒ near new shield with thickness of 200 µm

K.K. Gan

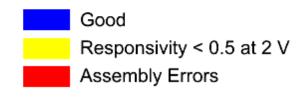

## PIN Opto-pack Production Experience

| Total        | 161 |

|--------------|-----|

| Good         | 153 |

| Responsivity | 3   |

| Assembly     | 5   |

95.2 %

- ULM arrays

- 2013/14 pre-production data

- produced 400 for opto-boards + 400 for RX 3.0% 1.8%

K.K. Gan

Pixel Opto Review

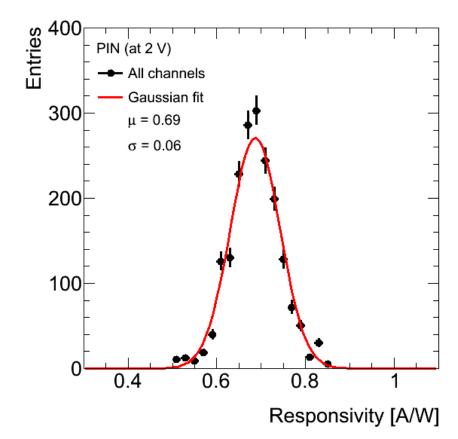

#### PIN Resposivity

- average PIN responsivity ~0.69 A/W

- require 0.5 A/W @ 2 V in QA

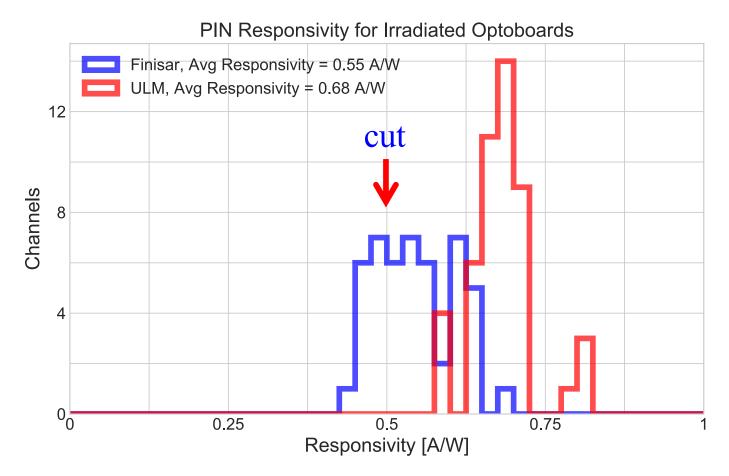

#### PIN Responsivity

#### • ULM PIN has higher responsivity

# VCSEL/PIN Array CostvcselPinFinisar\$188\$57ULM€28€16

- quotation based on 1000 VCSEL/500 PIN array

- Finisar announced end-of-life for VCSEL/PIN

- order by May 31

II-VI

• ULM: 2-3 months lead time due to shortage of VCSEL wafers

€70

- ULM VCSEL optical power is acceptable

- might be as good as Finisar with thiner shield

- ULM PIN responsivity is better than Finisar

- one ULM channel started to degrade at 140 hour and die at 250 hour but other 55 channels are alive for 1400 hours

- use ULM for both VCSEL and PIN arrays? K.K. Gan Pixel Opto Review

#### Summary of Proposal

• use opto-pack design used in 2<sup>nd</sup> generation opto-boards

- use ULM VCSEL/PIN arrays?

- follow the 2013/14 assembly/QA procedure