# WBS 6.1.3 Pixel Communication & Services

K.K. Gan Level-3 Manager & CAM The Ohio State University

U.S. ATLAS HL-LHC Upgrade Project DOE CD-1 Director's Review Brookhaven National Laboratory Upton, NY May 7-9, 2018

### Outline

- Technical Details

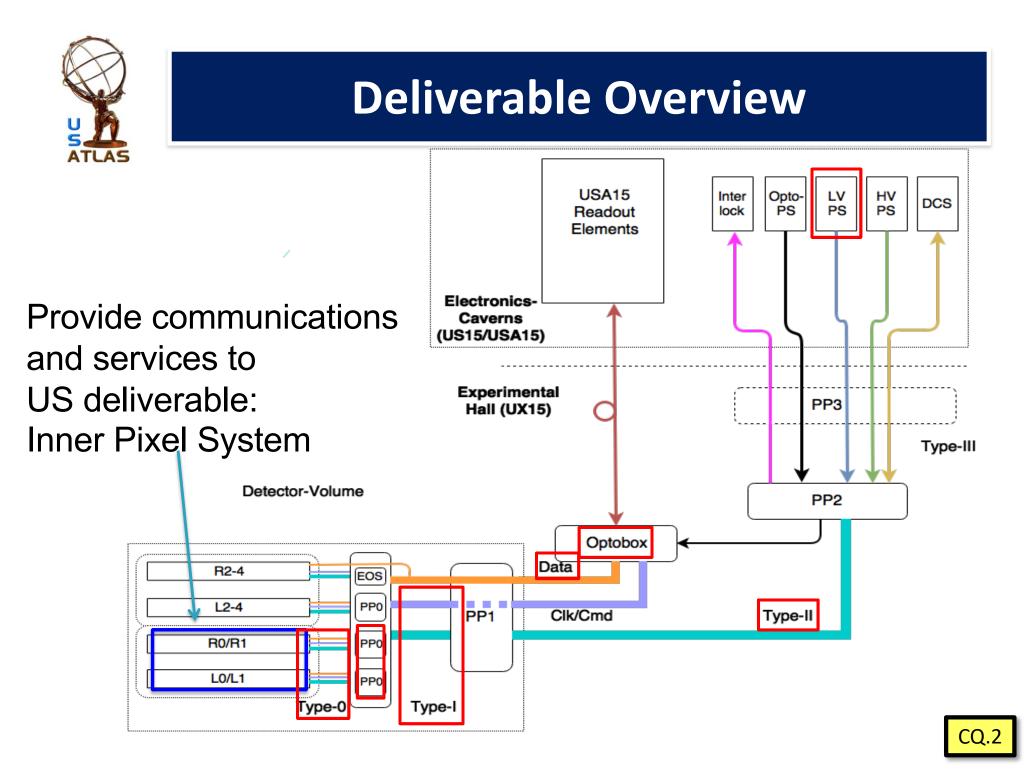

- Deliverable Overview

- R&D Status and Plans

- Project Management

- Management Structure: CAM and ICs

- Cost and Schedule Estimating Methodology

- ES&H

- Cost and Schedule

- Budget and Schedule estimates

- Risk and Uncertainty

- Closing Remarks

### **Technical Details**

- Institution: Oklahoma State

- 6.1.3.1: Flex Circuit

- design/prototype/production of flex circuits for transmission of command/clock, LV, HV, DCS (safety monitors)

- Challenge: high-speed transmission/low signal loss or voltage drop with minimum material

- Technical Specs (see later)

|                                | Production         | <b>Pre-Production</b> |

|--------------------------------|--------------------|-----------------------|

| Flexes needed for inner system | 300                |                       |

| Yield                          | 72%                |                       |

| Flexes to be produced          | 420                | 30                    |

| Total material cost            | \$245 <i>,</i> 000 | \$35,000              |

- Institution: SLAC

- 6.1.3.2: Patch Panel 0 (PP0)

- Design/prototype/production of PPO with connectors for data, command/ clock, LV, HV, DCS (safety monitors)

- challenge: minimum material and insertion loss in bandwidth/signal strength

| PP0 type         | Quantity | Components | PCB fab | Assembly | Total     |

|------------------|----------|------------|---------|----------|-----------|

| Data Barrel LO   | 96       | \$120      | \$14    | \$20     | \$14,784  |

| Data Barrel L1   | 120      | \$100      | \$14    | \$20     | \$16,080  |

| Data Endcap      | 648      | \$80       | \$14    | \$20     | \$73,872  |

| SP chains        | 264      | \$100      | \$14    | \$20     | \$35,376  |

| Total            |          |            |         |          | \$140,112 |

| Yield            |          |            |         |          | 85%       |

| Total inc. yield |          |            |         |          | \$164,838 |

CO.

- Institution: SLAC

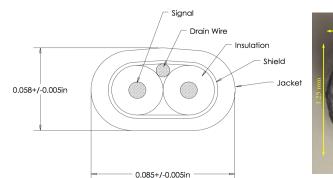

- 6.1.3.3: TwinAx

- Twin co-axial cables

- Need 864 bundles of four TwinAx cables

- Opto-box : soldering to mini-PCB with connector

- PPO: soldering to PPO for inner detector and to mini-PCB at outer detector

- Challenge: high-speed data transmission up to 5.5 m of skinny cables with acceptable attenuation

- Technical Specs (see later)

- Institution: UC Santa Cruz

- 6.1.3.4: Type-1 bundle

- design/prototype/production of cable bundles for command/clock, LV, HV, DCS (safety monitors)

- Challenge: compact bundles with connectorization of minimum loss

- Technical Specs (see later)

- Institution: Ohio State

- 6.1.3.5: Optical Carrier Board

- QA of optical carry boards designed by Bern

- Production of 280 boards, including 80% yield

- Technical Specs (see later)

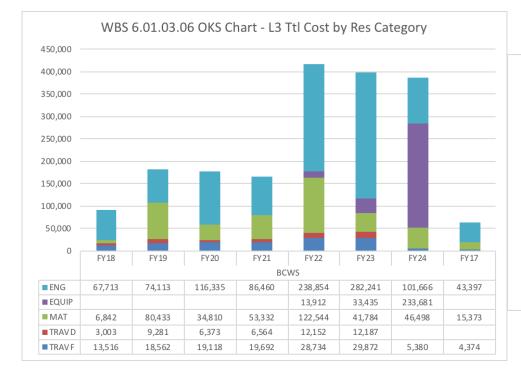

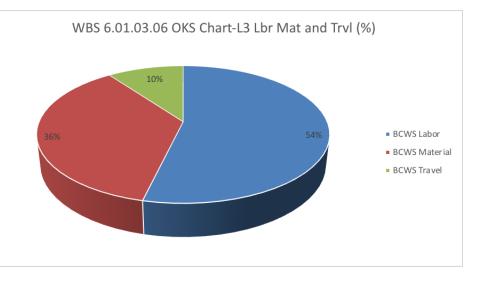

- Institution: Oklahoma State

- 6.1.3.6: Serial Power Supply

- design/prototype/production of power supplies, backplane, control system, chassis, Type-II cables

- Challenge: supply constant current up to 16 FE ASICs in series

- Technical Specs: supplies of constant current of 8 A per channel to the front-end chips with a voltage range of 1.2-1.5 V per chip

| Description                             | Production | <b>Pre-production</b> |

|-----------------------------------------|------------|-----------------------|

| Pixel Modules in the pixel inner system | 2456       |                       |

| Pixel Modules per power supply          | 8          |                       |

| Power supplies to be installed          | 307        |                       |

| Production yield                        | 90%        |                       |

| Power supplies to be produced           | 341        | 31                    |

| Description                             | Quantity |

|-----------------------------------------|----------|

| Cables needed in the pixel inner system | 142      |

| Production yield                        | 90%      |

| Cables to be produced                   | 158      |

- Institution: Southern Methodist U.

- 6.1.3.7: Equalizer ASIC

- design/prototype/production of equalizer ASIC

- Challenge: correct for degradation of high frequency component of the data signal after propagation through TwinAx

- Technical Specs: (see later)

### **Technical Specs**

- 6.1.3.1 (Type-0 Services), 6.1.3.2 (Patch Panel 0), 6.1.3.3 (Twinax Cables), 6.1.3.4 (Type-I Services) and 6.1.3.7 (Equalizer): radiation-hard data transmission from the modules to the optical converters at 5.12 Gb/s up to 5.5 meters with maximum attenuation of 20 dB.

- 6.1.3.5 (Opto-Links): optical converters for converting electrical data signals to optical signals for transmission to the DAQ system at 5.12 Gb/s per channel and vice verse for the clock/command signal at 160 Mb/s from the DAQ system.

- 6.1.3.6 (Serial Powering): Serial power supplies produce a constant current up to 8 A per serial power chain and provide a voltage of 1.5-2.0 V per module, with a maximum of 16 modules per chain.

- 6.1.3.1:

- Identified flex stack-up and materials. Preliminary layout completed. Production in FY20.

- 6.1.3.2:

- PP0: Initial conceptual design completed. Production in FY21.

- 6.1.3.3

- TwinAx: cables of different dielectric material and gauges prototyped. Currently evaluating a possible final prototype 30 AWG cable with much smaller cross section due to much reduced wire spacing. Production in FY20.

- 6.1.3.4:

- Study cross talk and breakdown voltage on Type-I cable bundle. Production in FY20.

- 6.1.3.6:

- Tested serial powering with several FE-I4 chips. Production in FY23.

- 6.1.3.7:

- Design of equalizer circuit and clock recovery circuit started. Production in FY20

## **Project Management**

- 6.1.3.1+6.1.3.6: flex circuit and power supply

- Oklahoma State: F. Rizatdinova leads the effort with S. Welch as the lead engineer at cost.

- Cost estimate mostly based on quotes and data from previous hardware development projects

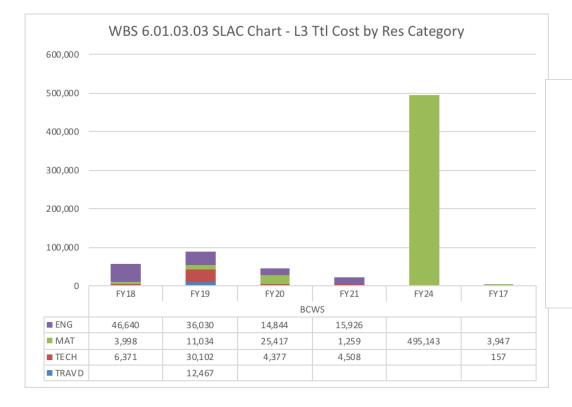

- 6.1.3.2+6.1.3.3: PPO/TwinAx

- SLAC: Su Dong leads the effort with contributions from physicists plus engineers and technicians available at cost.

- TwinAX cost estimate based on several years of R&D and PPO based on fabricating similar objects for Insertable Barrel Layer (IBL) of ATLAS

Pixel detector

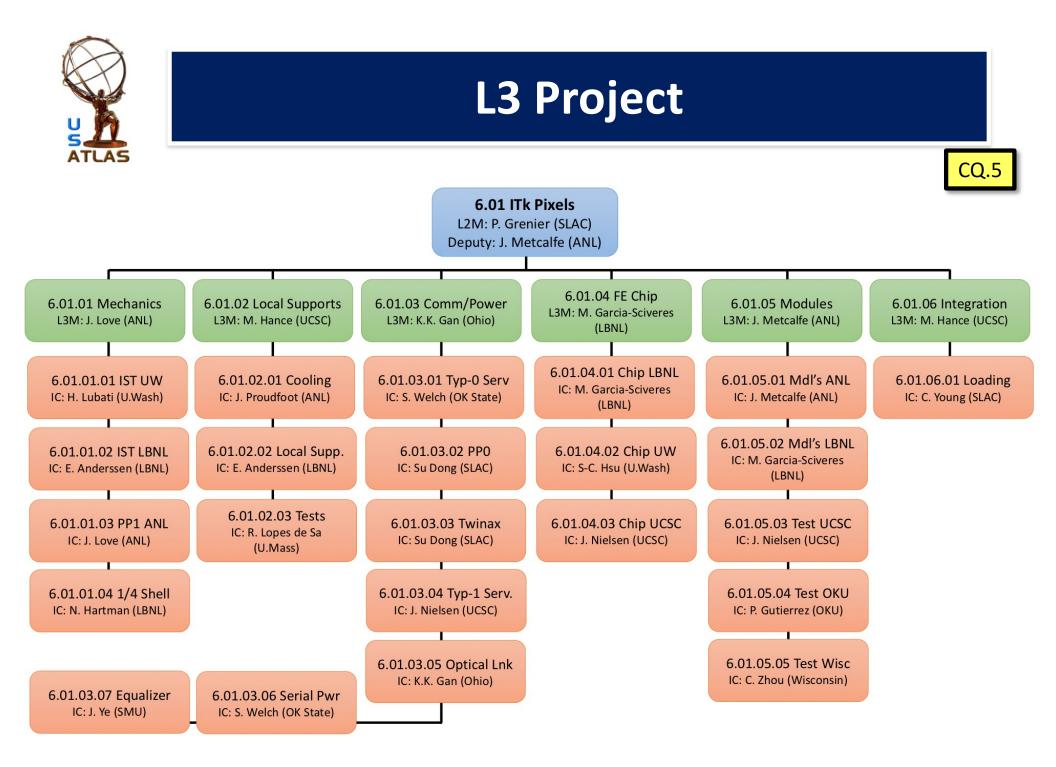

### L3 Project

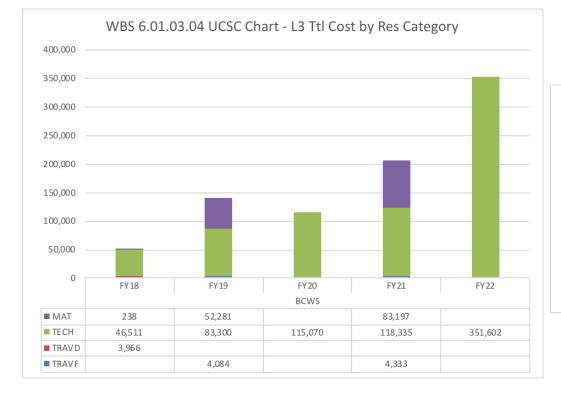

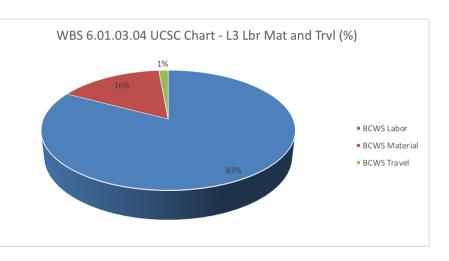

### • 6.1.3.4: Type-I bundle

- UCSC: J. Nielson leads the effort with contributions from physicists plus engineers and technicians at cost.

- Cost estimate based on similar objects for Insertable Barrel Layer (IBL) of ATLAS Pixel detector

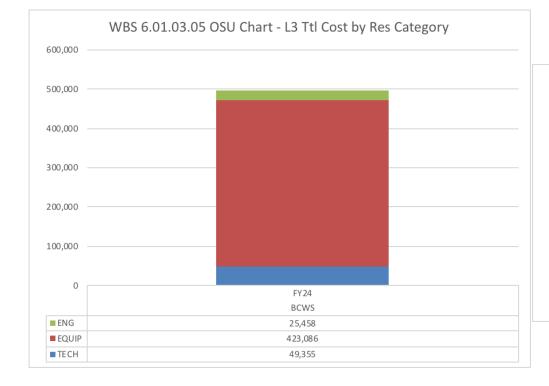

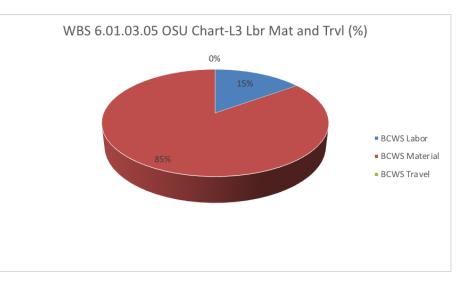

### • 6.1.3.5: Opto carrier board

- Ohio State: K.K. Gan leads the effort with contributions from physicists plus engineers and technicians at cost.

- Cost estimate based on building two generations of opto-boards for the Pixel detector of ATLAS

- 6.1.3.7: Equalizer

- SMU: J. Ye leads the effort with contributions from engineers and technicians at cost.

- Cost estimate based on design/prototyping of other ASICs

- Safety is of the highest priority within the Project

- Work at each institute adheres strictly to its ES&H policies

| Institute      | Institute ES&H Contact                                                       |

|----------------|------------------------------------------------------------------------------|

| Ohio State     | M. St. Clair (https://ehs.osu.edu)                                           |

| Oklahoma State | K. Southworth (https://ehs.okstate.edu)                                      |

| SLAC           | C. Fried (http://www-group.slac.stanford.edu/esh/)                           |

| SMU            | B. Chance (https://www.smu.edu/BusinessFinance/RiskManagement/Health-Safety) |

| UC Santa Cruz  | L. Wisser (https://ehs.ucsc.edu)                                             |

- The BNL ES&H Liaison provides oversight and advice

- US ATLAS HL-LHC Institute Contacts act as interfaces between their institute and BNL and CERN

- Main Hazards for this Deliverable

- Radiation: CERN test beams are in controlled areas

- All work done in compliance with safety policies at the institute or CERN

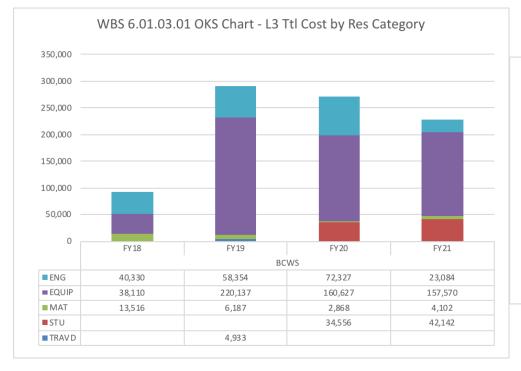

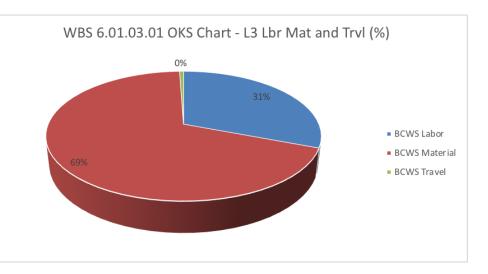

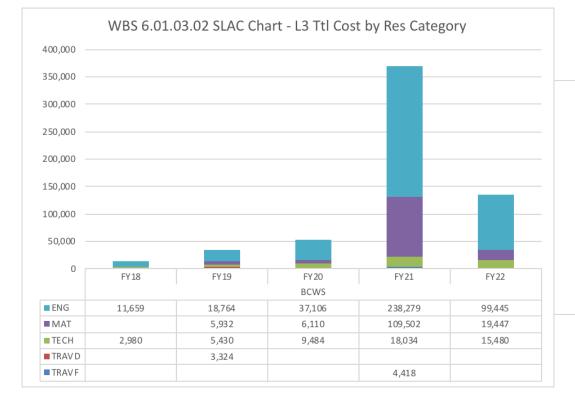

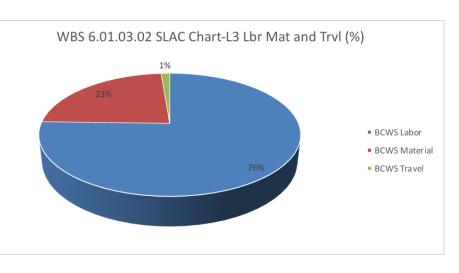

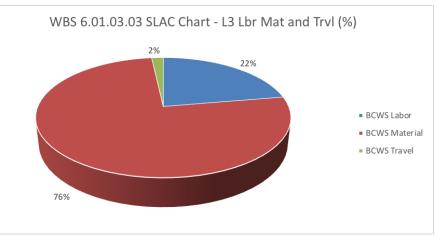

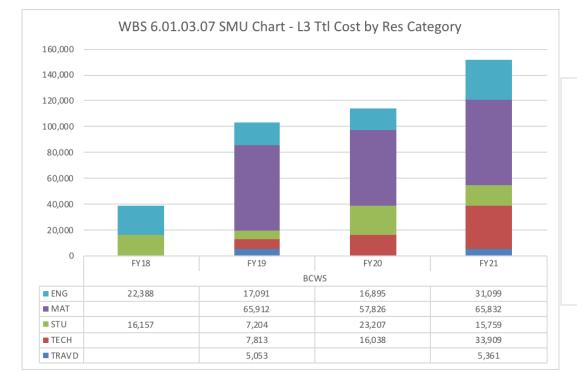

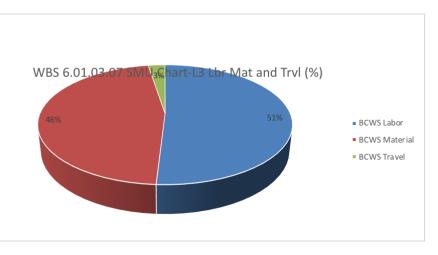

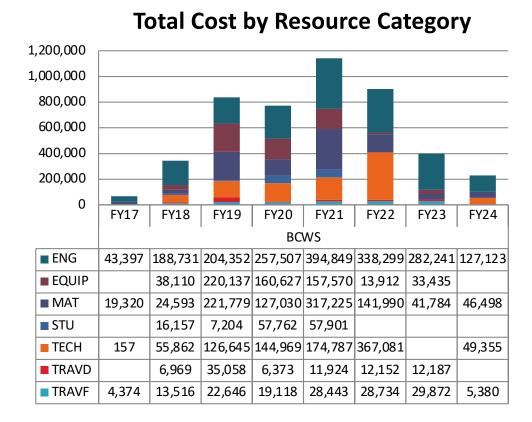

### **Cost and Schedule**

CQ.4

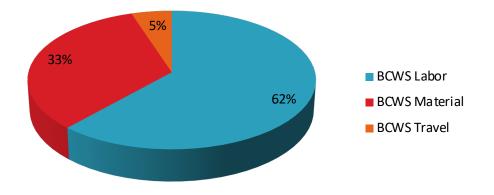

#### Labor, Material and Travel (%)

### Schedule

### • Items needed at SLAC integration in 2022:

- 6.1.3.1: flex circuits

- 6.1.3.2: PPO

- 6.1.3.3: TwinAx

- 6.1.2.4: Type-I bundles

- Items needed at CERN in 2024:

- 6.1.3.5: opto carrier boards

- 6.1.3.6: serial power supplies

- 6.1.3.7: equalizer

- Main external dependencies:

- System test: data aggregator ASIC + cables + opto-links for operation at 5.12 Gb/s

### **Risk and Uncertainty**

• RD-06-01-03-001: 5 Gb/s data transmission speed not achievable

- Response: use slightly larger twinax cables or double the number of data cables to operate at 2.56 G/s, and/or operate at lower bandwidth and make use of data compression.

- Mitigation: allocate more resource in connectorization

- Cost: \$9K-\$12K

- Delay: 2-4 months

### • RD-06-01-03-002: Serial powering fails to meet specifications

- Response: allocate more resource for prototyping and use new cables instead of the existing cables.

- Mitigation: More prototyping of power supply and study of the cooling requirement

- Cost: \$70K-\$120K

- Delay: 2-4 months

### Milestones

- FY19: Flex FDR

- FY19: TwinAx FDR

- FY19: Type-1 bundle FDR

- FY20: Flex PRR

- FY20: TwinAx PRR

- FY20: Type-1 bundle PRR

- FY21: PP0 FDR

- FY21: PP0 PRR

- FY22: power supply PDR

- FY23: power supply PRR

## **Closing Remarks**

- Communication and Services WBS contains both active and passive deliverables

- Some R&D are well advanced and others just started

- Main technical challenge:

- Achieve 5.12 Gb/s data transmission at up to 5.5 m of cables plus connectors with less then 20 dB of attenuation

### **Bio Sketch of L3 Manager**

- K.K. Gan, Professor of Physics, The Ohio State University

- Member of ATLAS since 1998

- Leading the design and fabrication of two generations of optical links for the ATLAS pixel detector

## **Institute Capabilities**

- 6.1.3.1, 6.1.3.6, Oklahoma State:

- Good facility for electronics development and fabrication

- One engineer available at cost

- Previously involved in the Insertable B-Layer pixel project

- 6.1.3.2, 6.1.3.3, SLAC:

- Large facility for electronics development and fabrication

- Large pool of engineers and technician available at cost

- Previously involved in the Insertable B-Layer pixel project

- 6.1.3.4, UC Santa Cruz:

- Good facility for electronics development and fabrication

- Pool of engineers and technician available at cost

- Previously involved in the Insertable B-Layer pixel project

- 6.1.3.5, Ohio State:

- Clean room with automatic wire bonders and probe stations etc

- Two engineers available at cost

- Previously leading two ATLAS pixel opto-link projects

- 6.1.3.7, Southern Methodist:

- Good facility for optical electronics development

- Engineers available at cost

- Previously leading ATLAS LAr opto-link projects