## Status of Opto-Board Development

K.K. Gan The Ohio State University February 16, 2004

K.E. Arms, K.K. Gan, M.O. Johnson, H.P. Kagan, R.D. Kass, A. Rahimi, C. Rush, R. Ter-Antonian, M.M. Zoeller The Ohio State University

> A. Ciliox, M. Holder, S. Nderitu, M. Ziolkowski Universitaet Siegen, Germany

## Outline

- Introduction

- Opto-Board Design

- Prototype Results

- Irradiation Results

- Conclusions

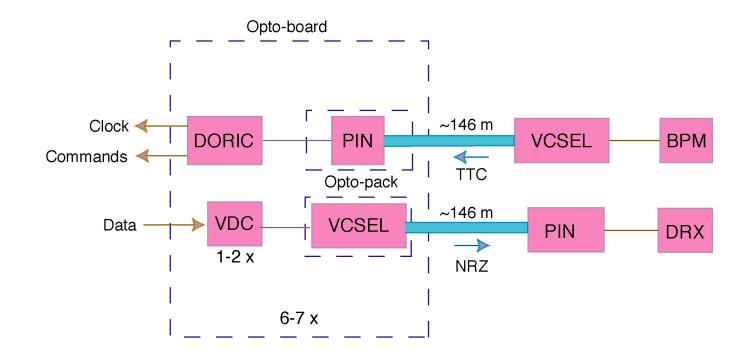

## Opto-link

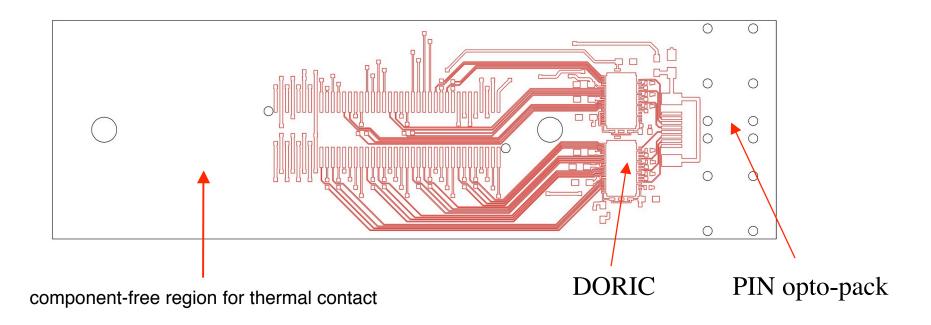

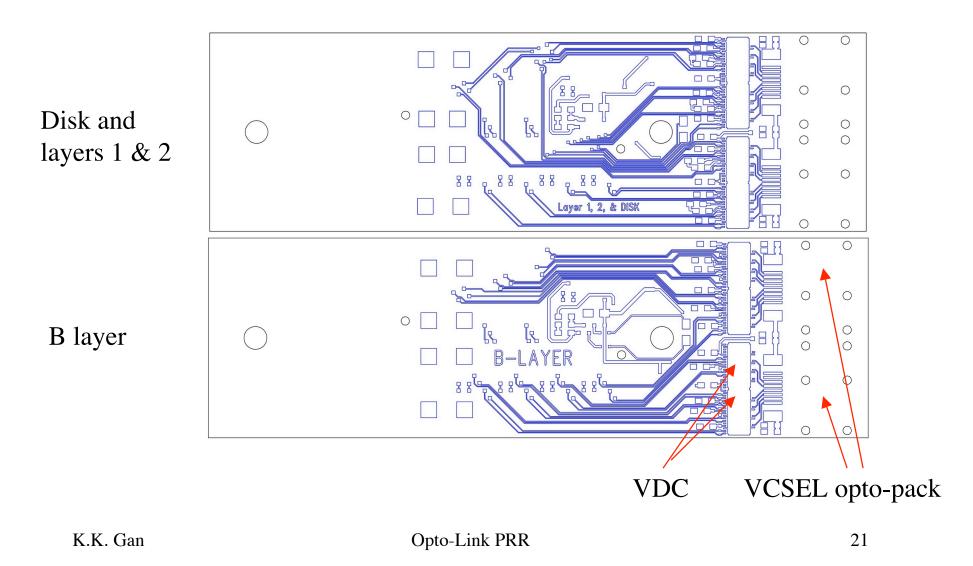

## Opto-Board

- converts: optical signal  $\leftarrow$  electrical signal

- provide 7 optical links:

- ☆ disks and 50% of layers 1 and 2 use 6 optical links

- two flavors:

- ☆ disk, layers 1 and 2:

- ◆ 2 x 4-channel DORIC + 8-channel PIN opto-pack

- ◆ 2 x 4-channel VDC + 8-channel VCSEL opto-pack

- ☆ B layer:

- ◆ 2 x 4-channel DORIC + 8-channel PIN opto-pack

- ◆ 4 x 4-channel VDC + 2 x 8-channel VCSEL opto-packs

- use BeO for heat management but prototype initially in FR4 for fast turnaround and cost saving

- have four FR-4 prototype runs to accommodate

various design changes in chips/opto-packs

- quantity needed: 212 opto-boards for two-hit system K.K. Gan Opto-Link PRR

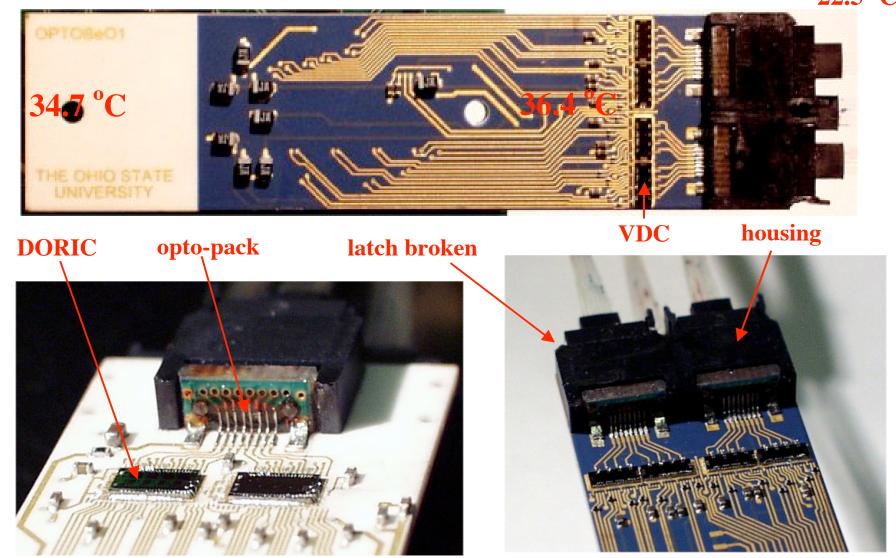

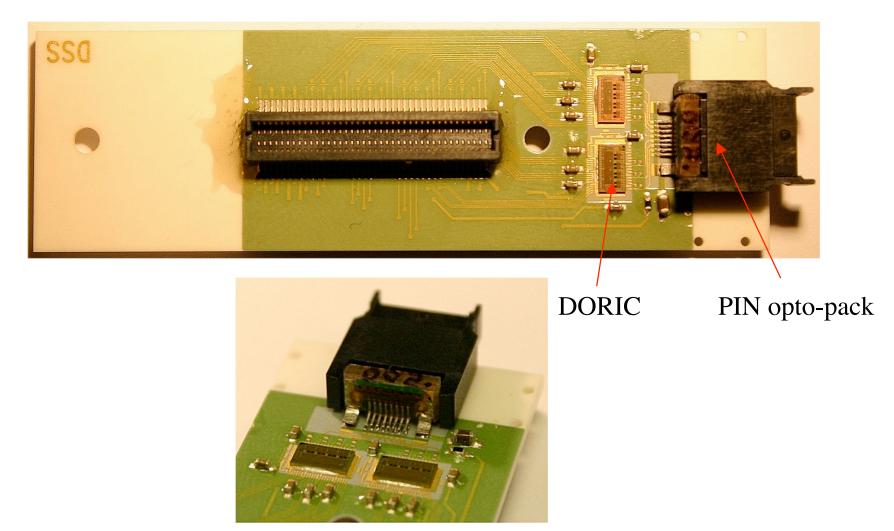

## BeO Opto-board Prototype I

- First batch:

- **30** boards delivered in April 2003

- several open vias on each board due to insufficient gold filling

repair with wire-wrap wires

- ⇒ working board with low PIN current thresholds for no bit errors

VDC-I5 opto-pack

## BeO Opto-board Prototype I

- Second batch:

- 31 boards delivered in June 2003

- vias overfilled and excess metal ground away

no open vias

- 17 boards have shorts between power and ground lines

- boards with no shorts have low PIN current thresholds for no bit errors

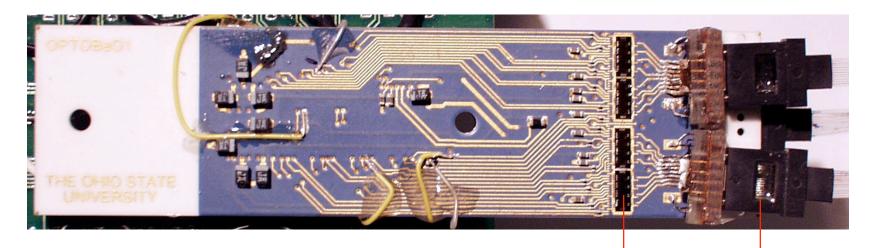

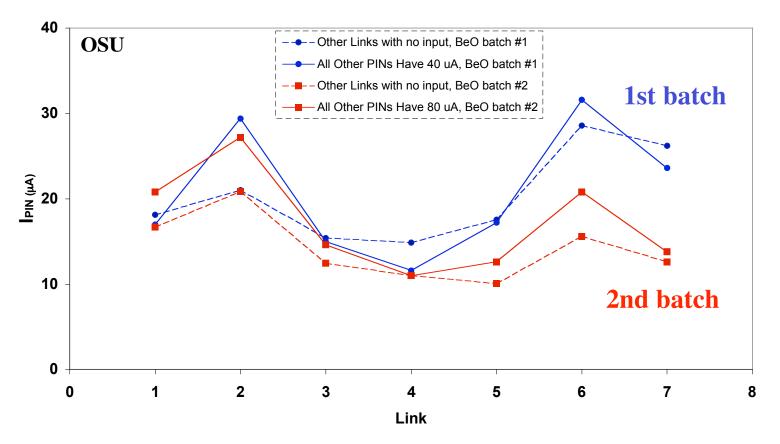

## BeO Opto-board Prototype I (2nd Batch) Ambient: 22.5 °C

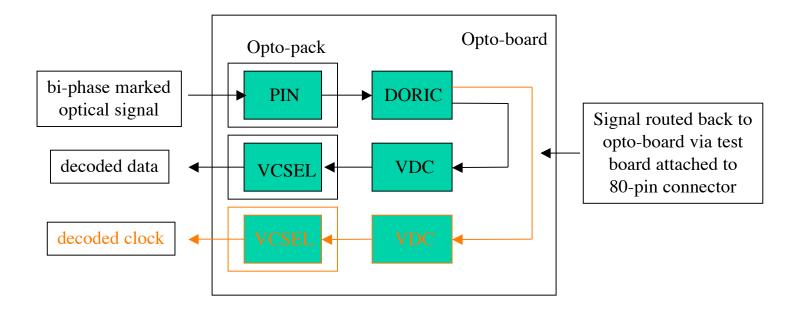

#### Opto-Board Testing with Loop-Back

# compare transmitted and decoded data measure minimum PIN current for no bit errors

### PIN Current Thresholds for No Bit Errors

both opto-boards have low PIN current thresholds for no bit errors independent of activity in adjacent channels

#### Proton Irradiations at CERN

- use 24 GeV protons at T7

- three irradiations of 0.25 µm chips since 2001:

- ☆ cold box: purely electrical testing of chips with no optical components

- ☆ shuttle: loop-back testing of opto-links on opto-boards

- ☆ last irradiation is August 2003

- ♦ 4 BeO opto-boards were tested in shuttle

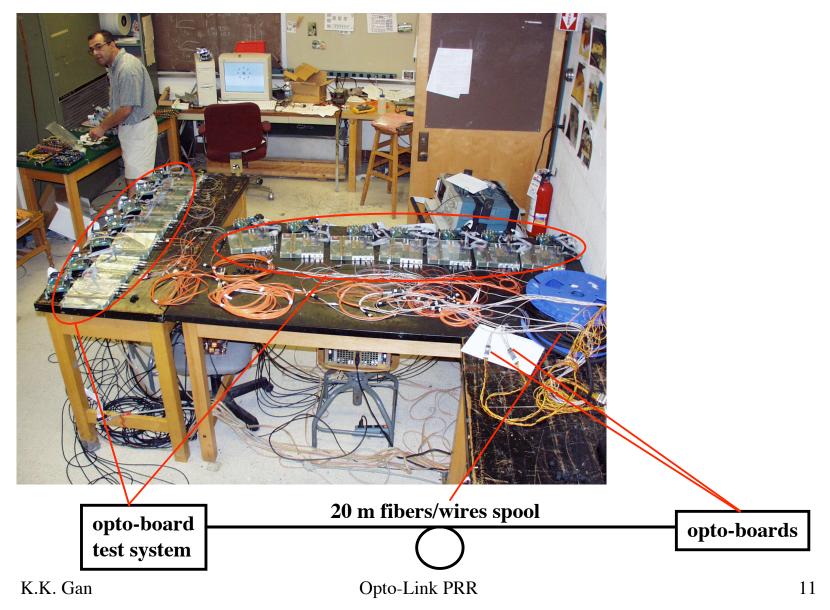

#### Shuttle Irradiation System

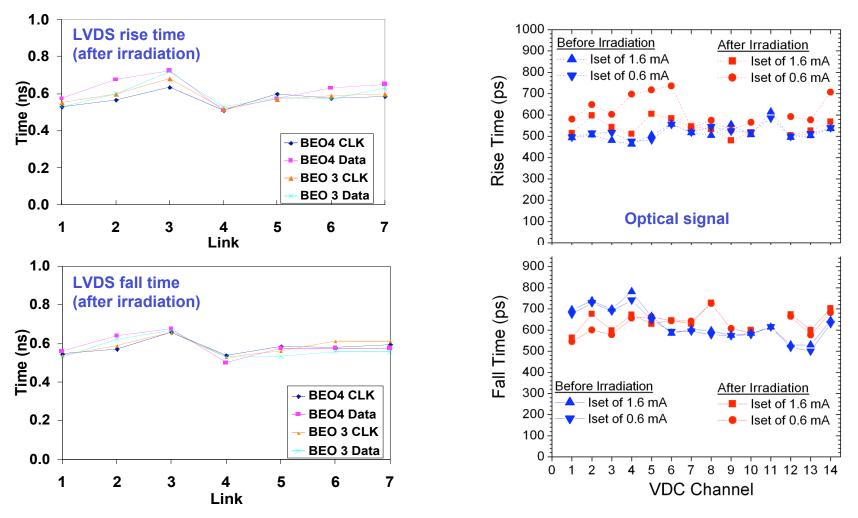

## LVDS and Optical Rise and Fall Times

$\checkmark$  rise and fall times after irradiation < 1 ns

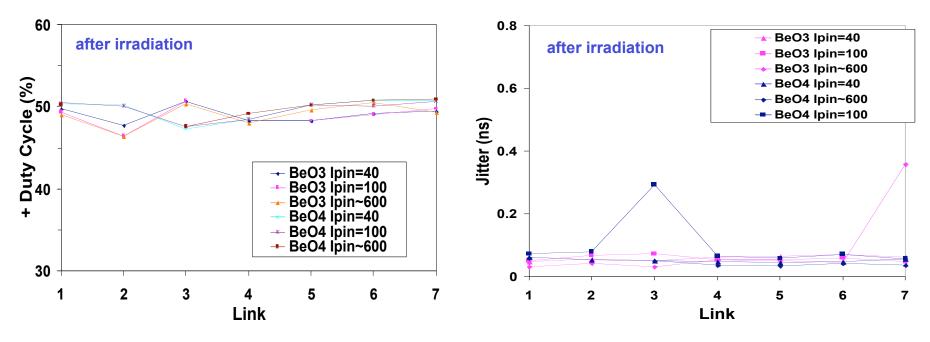

## Clock Duty Cycle and Jitter

✓ duty cycle: (50 ± 4)%

✓ jitter < 1 ns</li>

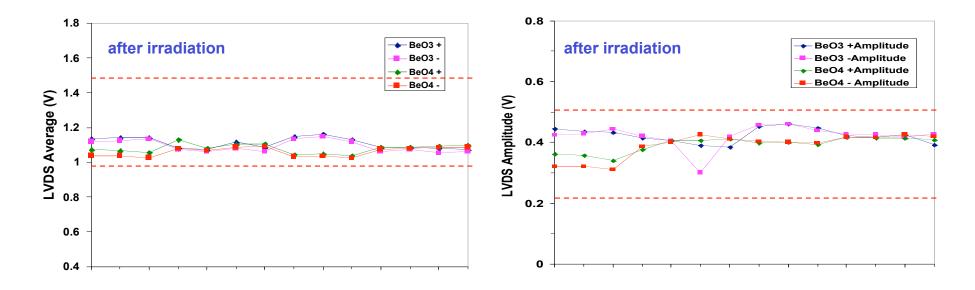

#### Clock LVDS Average and Amplitude

✓ clock LVDS average and amplitude are with spec.

✓ similarly for command LVDS

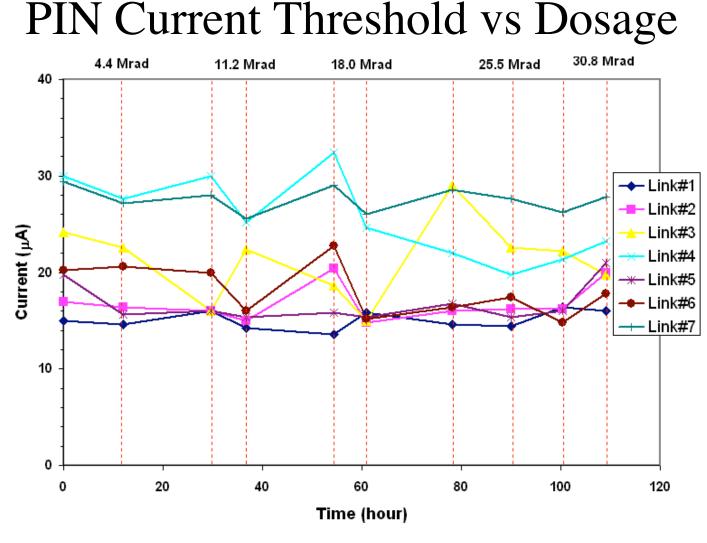

• PIN current thresholds for no bit errors remain constant

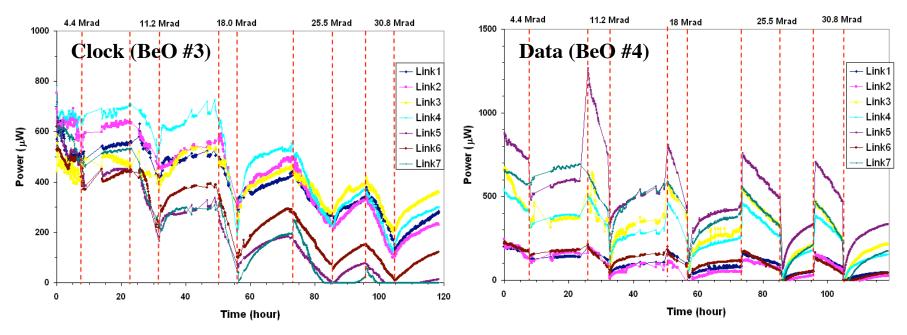

#### Optical Power vs Dosage

• power decreases with dosage as expected

annealing at ~ 13 mA recovers some lost power

- some channels have low power at beginning:

- ~35% power loss from 50  $\mu$ m SIMM to GRIN

- loss due to heating with all channels on

K.K. Gan

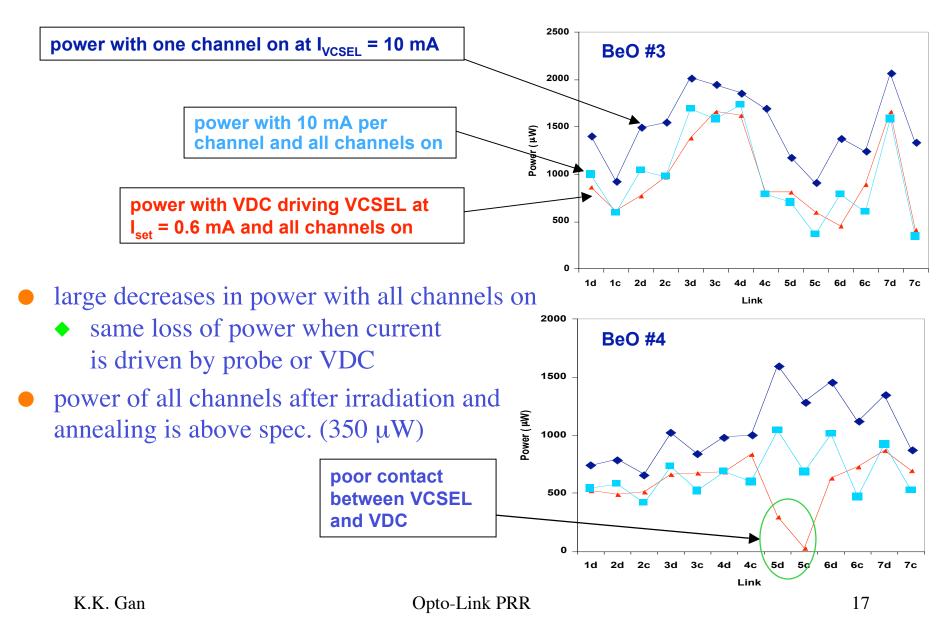

## Optical Power with One/All Channels On

## Summary on BeO Opto-Board Prototype I

- 7 opto-boards have been populated

- all opto-boards satisfy QA even after irradiation to 30 Mrad

- 5 opto-boards have good optical power (~1 mW or above)

- two opto-boards have lower power but still above spec. after irradiation

- ➡ demonstrate that we can fabricate opto-boards of high quality

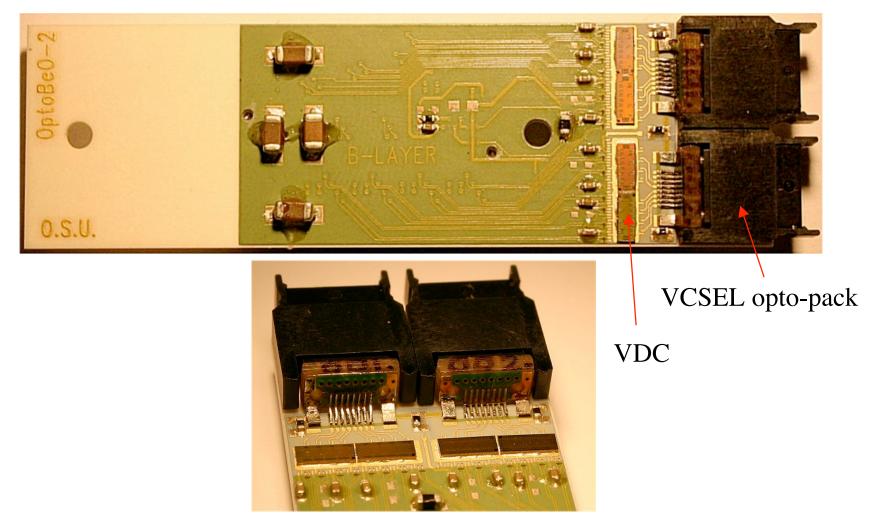

## BeO Opto-Board Prototype II

- fabricate two opto-board flavors instead of one in prototype I

- Iayers 1, 2 and disk:

- each pixel module uses one link for transmitting data

- ➡ VCSEL opto-pack serves 7 links (7 modules)

- B layer:

- each pixel module uses two links

- in same fiber ribbon for transmitting data

- ➡ VCSEL opto-pack #1 serves 8 links (4 modules)

- ➡ VCSEL opto-pack #2 serves 6 links (3 modules)

- use more experienced/expensive vendor

- fabricated several types of BeO boards for CDF

#### BeO Opto-Board Prototype II (Bottom)

#### BeO Opto-Board Prototype II (Top)

#### BeO Opto-Board Prototype II (Top)

#### BeO Opto-Board Prototype II (Bottom)

#### Production Plan

- 13/2/04: delivery of 14 opto-boards of each flavor

populate one board of each flavor to verify design

- 27/2/04: ship 10 boards of each flavor to Advanced Assembly Inc for passive components mounting

- 5/3/04: delivery of boards by Advanced Assembly Inc

- 5/4/04: complete production of prototype opto-boards

- start production of 300 opto-boards at CPT

- 5/6/04: delivery of production opto-boards by CPT

- 5/7/04: delivery of opto-boards with passive components

- 5/11/04: complete production of opto-boards (2 opto-boards/day)

#### **Production Procedure**

- mounting of passive components by Advanced Assembly Inc

- mechanical tolerance test

- electrical short test

- mounting of DORIC/VDC

- mounting of opto-packs/housings

- wire bonding

- basic functionality test

- encapsulation

- burn-in @ 50°C for 3 days/10 thermal cycles between @-25 & 50°C

- basic functionality test @-25 & 50°C and QA @ 10°C

## Production Site/Experience/Personnel

#### • site: OSU and Siegen

- experience:

- OSU: fabricated FR4 opto-boards + 5 BeO opto-boards

- populated 150 BeO boards with 0.5 million wire bonds for CLEO III

- use automatic wire bonder in-house

- Siegen: fabricated FR4 opto-boards + 2 BeO opto-boards

- use automatic wire bonder at Bonn

- personnel:

- OSU: 1 physicist (+ 1 vacancy) + 2 technicians + 2 p.t. technicians

- + 2 undergraduate workers

- Siegen: 2 physicists + 1 graduate student + 1 technician

- + 2 undergraduate workers

- OSU will perform mechanical/short for Siegen

## Summary

- has fabricated seven BeO opto-boards from prototype I

opto-boards pass QA even after irradiation up to ~30 Mrad

- BeO opto-boards from prototype II have been received

ready for production if no design error is found