### New Results on Opto-Electronics

K.K. Gan The Ohio State University

June 17, 2003

K. Arms, K.K. Gan, M.O. Johnson, H.P. Kagan, R.D. Kass, A. Rahimi, C Rush, R. Ter-Antonian, M. Zoeller The Ohio State University

A. Ciliox, M. Holder, S. Nderitu, M. Ziolkowski Siegen University

# Outline

VDC-I5

VDC/DORIC-I5e

QA

BeO Opto-board

Summary

- higher bright current as redesigned

- dim current close to target 1 mA

- rise/fall times, duty cycle, current consumption all within specs K.K. Gan ATLAS Pixel Week 3

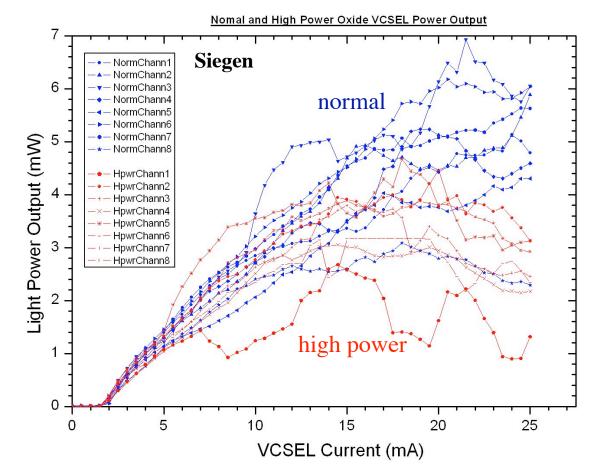

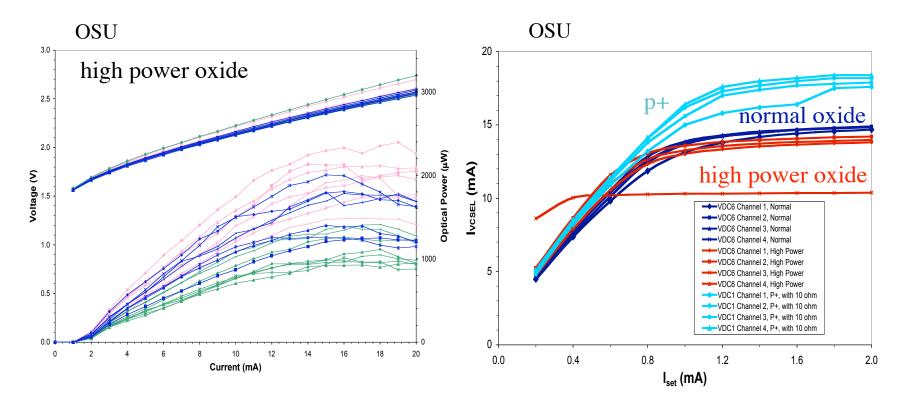

#### Optical Power of Normal & High Power Oxide VCSELs

• both kinds of VCSELs produce similar optical power

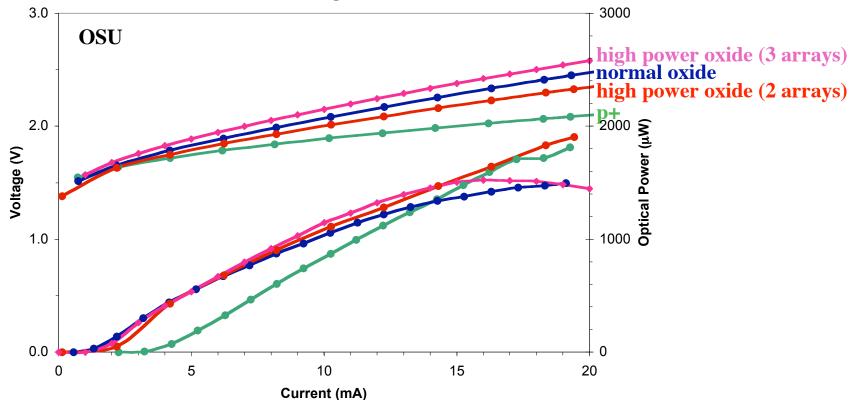

#### I-V Curves/Optical Power of P+, Normal & High Power Oxide VCSELs

- p+/oxide VCSELs have similar optical power in operating range (10-20 mA)

- oxide VCSELs have larger effective serial resistance

- ⇒ smaller VCSEL current when driven by VDC

K.K. Gan ATLAS Pixel Week

• high power oxide VCSEL has lower maximum current: 15 mA

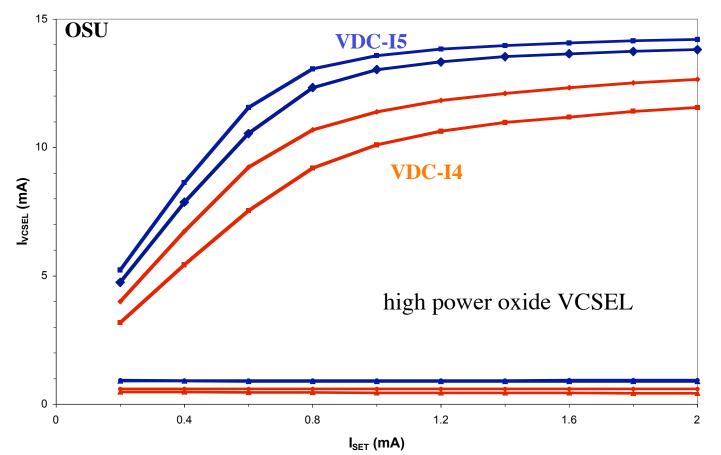

#### I-V Curve of High Power Oxide VCSELs

some VCSEL arrays contain a channel with much larger effective serial resistance

4 mA less VCSEL current when driven by VDC

## VDC/DORIC-I5e: Engineering Run

- convert from 3-metal to 5-metal layout

- minor improvements in DORIC:

- ★ default power distribution layer is

- now the 3rd layer and hence thinner

- ⇒ thicken power/ground lines

- ★ add MIMCAP bypass capacitors to power lines

⇒ reduced noise in internal signals

- ★ add ground plane over digital circuit as noise shield

- signal is slightly slower due to stray capacitance to shield

- ★ convert reset from active high to low for ease of implementation by DCS

- $\Rightarrow$  slightly better performance at  $\pm 3\sigma$  corner transistor parameters

- submitted with MCC in April 2003

- status: wafer @ Bonn

#### VDC/DORIC/Opto-board Quality Assurance

- circuit boards: designed/built/tested

- LabView programs: written/tested

- DORIC passes QA

- opto-board passes QA

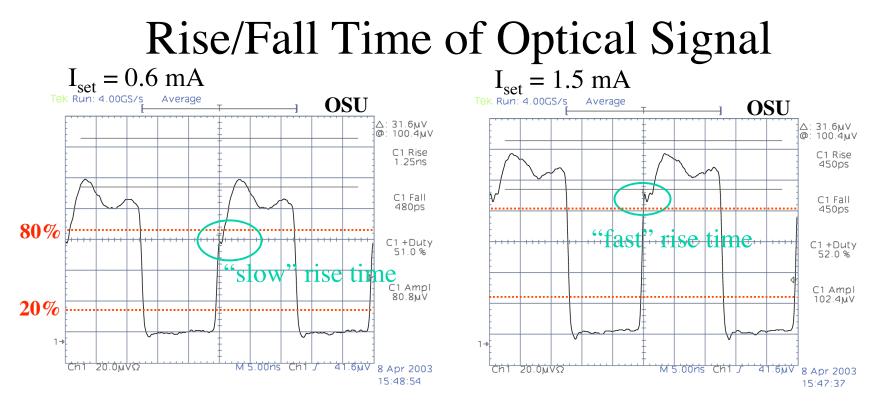

- rise time of optical signal: < 1 ns</p>

- VDC fails following QA:

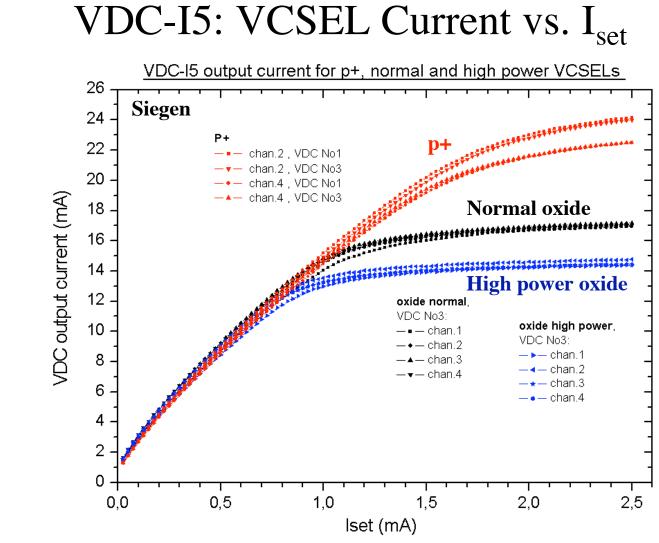

- VCSEL current at  $I_{set} = 1.5 \text{ mA}$ : 15 mA vs. 20 mA in QA

- ⇒ redefine spec in QA for high power oxide VCSEL?

- rise time of optical signal: ~ 1.5 ns vs. < 1 ns in QA

- ★ slower rise time due to a kink in signal and long leads in test board

⇒ define rise/fall time as time duration for the signal to rise/fall from 20 to 80% instead of 10 to 90% of the amplitude

■ both 10-90 and 20-80% are widely used by industry

- ★ VDC passes opto-board QA

⇒ redefine spec in VDC QA K.K. Gan

10

## QA Plans

- VDC/DORIC QA:

- current use packaged chip to exercise QA system

- just received probe cards

- ⇒ perform QA with probe station

- opto-board QA:

- perform QA in temperature controlled chamber

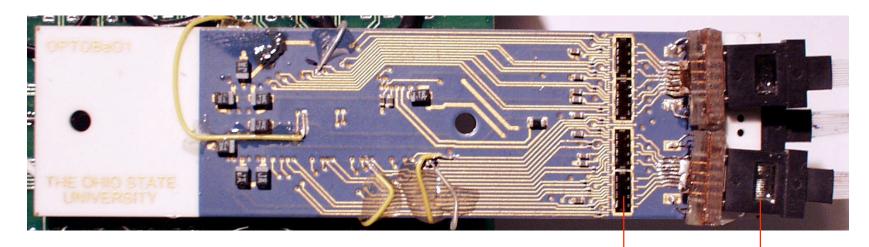

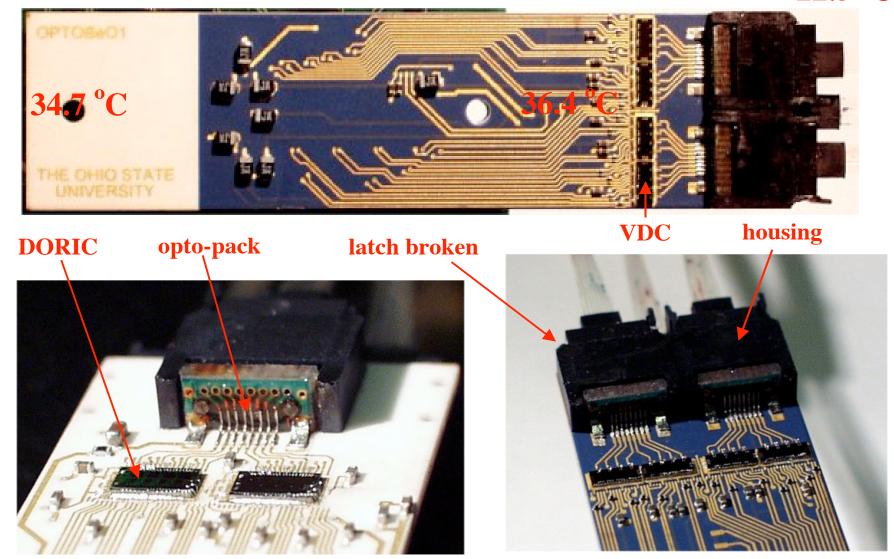

### Status of BeO Opto-board

#### • First batch:

- 30 boards delivered in April

- several open vias on each board due to insufficient gold filling

repair with wire-wrap wires

VDC-I5 opto-pack

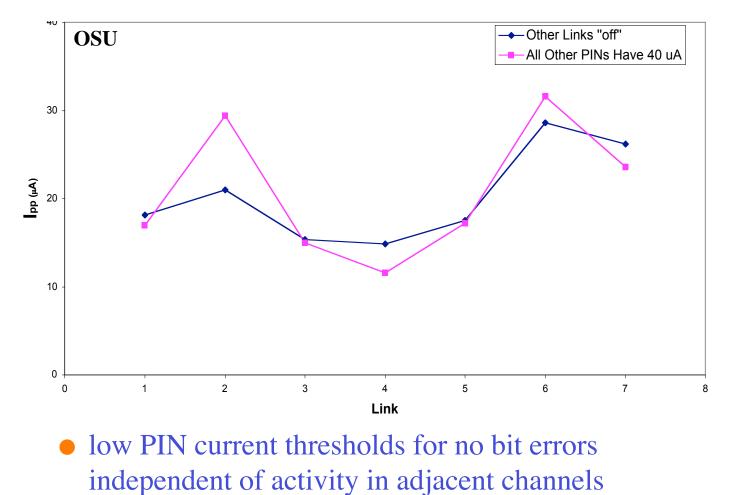

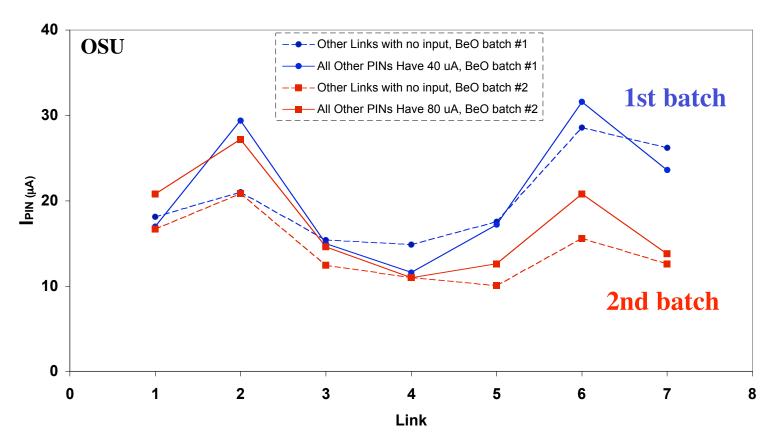

#### PIN Current Threshold for No Bit Errors

**BeO Thresholds**

⇒ no design error

## Status of BeO Opto-board

- Second batch:

- 31 boards delivered in June

- vias overfilled and excess metal ground away

no open vias

- 17 boards have shorts between power and ground lines

- attempt to populate a second BeO board:

- opto-pack housing fits well

- opto-pack must be delivered with pins bent by 90° and flush with opto-board

- one DORIC mounted backward

- no visible damage to adjacent chip after replacement

- board failed to work

- ⇒ replaced both DORICs

# BeO Opto-board from 2nd Batch Ambient: 22.5 °C

K.K. Gan

#### PIN Current Threshold for No Bit Errors

- both opto-boards have low PIN current thresholds for no bit errors independent of activity in adjacent channels

- awaiting quote from a second vendor

K.K. Gan ATLAS Pixel Week

### Summary

- all improvements in VDC/DORIC-I5 are successful

- VDC/DORIC/opto-board QA procedures exercised

- BeO opto-boards fabricated from 1st and 2nd batches operate with low PIN current thresholds with no bit errors