CMS Endcap Muon DDU Homepage

CMS Endcap Muon DDU Homepage

What is it?

The DDU is the "Detector Dependent Unit" and serves as the interface point between the customized front end electronics of the Endcap Muon (EMU) Cathode Strip Chambers (CSCs) and the main data acquisition system of the Compact Muon Solenoid (CMS) detector. More information is available regarding DDU scope, basic operation, and historical DDU prototype information.

- EMU DDU details:

- DDU operation and Data Format

- EMU DAQ buffer and event size summary (DMB-DDU-DCC, for Attila Racz/RUWG)

- Technical PCB details (for UF Track Finder)

- Historical DDU prototype references

- Current (May 2002) EMU occupancy and data volume estimates (Gilmore, Acosta)

- Old (Oct. 2000) EMU event rate and data volume estimates (Nylander, Kim)

- DDU firmware schematic files (VMEfpga, CtrlFPGA, InputFPGA)

- DDU firmware SVF files (vme5ctrl, ddu5ctrl_1 & 0, in5ctrl_1 & 0)

- DDU PCB design directory (for TF design at UF)

- CMS Homepage (CERN)

- Draft of CMS Raw Data Formats note

- OSU CMS Group Homepage

- CMS Endcap Muon Electronics Homepage (EMU)

- CMS Readout Unit Working Group Page (RUWG)

- Status Reports (pdf files):

- April 2004 EMU Meeting, OSU Columbus: DDU 2004 Status

- Oct 2003 EMU Meeting, Carnegie Mellon: New DDU & DCC Development

- March 2003 EMU Meeting, UF Gainesville: CFEB, DMB & DDU Status

- June 2002 CMS Week DAQ, RUWG and EMU: DDU Status (15 input DDU w/S-Link64 output)

- April 2002 EMU Meeting, UF Gainesville: DDU Status (15 input VME64 DDU with gigabit output)

- Jan 2002 EMU Meeting, Rice Houston: DDU Status (4 input DDU with gigabit output)

- June '99 CMS Week, FERU Workshop: DDU Status (old style PCI DDU prototype)

- June '99 CMS Week, FERU Workshop: CSC FE Integration (old style PCI DDU prototype)

- Mar '99 FERU Workshop: DDU Status (old style PCI DDU prototype)

DDU

Operation

General Hardware

Info, Production DDU

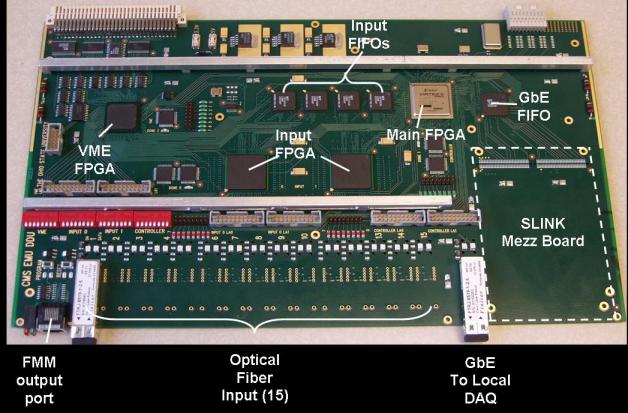

The final Production DDU (small & red) is a 220 mm 9U VME64x board. It takes in data from 15 EMU DAQ Motherboards (DMB) on 15 1.6 Gbps fiber optic cables (1 fiber per DMB) via high-density (LC) front panel inputs (Finisar FTRJ-8519-1-2.5). The data from each fiber gets deserialized by the Rocket IO within 2 Xilinx FPGAs (XC2VP20-FG676-6C) and stored in internal Block RAM FIFOs and 8 larger external FIFOs (TI 74LV3690-6). For every L1A trigger, the DDU cycles through the stored data for 15 DMBs in order (0 to 14), and sends out the entire event record to the main CMS readout via the DCC/SLINK and through the gigabit Ethernet fiber for local PC readout (EMU SPY/standalone DAQ). As it processes data, the DDU Control FPGA (Xilinx XC2VP7-FF672-6C) performs synchronization and status monitoring, data integrity and error checking. The Production DDU Data Format is compatible with the main CMS DAQ, as defined in the CMS Common Data Format. The DDU is capable of processing data at a sustained rate of over 600 MB/sec.

Technical Operation

Details

The DDU begins processing an event after the L1A has been received and at least one data word has been received from each of the 15 DMB fiber inputs. The DDU then does a quick scan of the first word of the event from each DMB to determine if CSC data is present, followed by full processing of all the remaining data from those DMBs that have additional event data, culminating in the transmission of all event data to the CMS readout system via S-LINK64 on the DCC. In this way, the DDU completes the data readout for the event from each DMB before processing the next event.

All data processed by the DDU is passed through to the main readout with one notable exception; the DMB Lone word (tagged by DDU Code word 8) from each DMB "No Data" event is always removed at the DDU during the quick scan as a form of zero-suppression, without being forwarded to the readout system. The information from this word is used for event consistency checks and control within the DDU, the results of which are ultimately summarized in the DDU event header. All other DMB-DDU data words are transmitted unchanged to the DCC/SLINK readout system within the DDU event packet.

Event processing in the DDU includes event and bunch crossing number checking, word count and CRC verification, data consistency checks, status monitoring for busy/full/warning/error conditions, Fast Monitoring communications via the FMM, and S-Link64 data formatting for the main CMS DAQ. Data can also be passed (in parallel or exclusively) to the dedicated EMU standalone readout system (SPY path) via gigabit Ethernet from each DDU. This will be useful for calibration, spy data, and other standalone checking/debugging tests when running in the local EMU partition.

DDU

Data Format

- Early Prototype DDU Format: Input from DMB,

Output from DDU

- FOV==0,

used in May 2003 - June 2004 beam tests; still used at UCLA

- Second Prototype DDU Format: Input from DMB, Output from DDU

- used

Oct. 2004 to Sept. 2005 for Slice & beam tests; used for 2 DDUs at

SX5

- FOV==3

for big red DDU at SX5; FOV==4 for small green DDU at SX5

- format

change summary:

- DMB

First Header words swapped (1c->1b, 1b->1a, 1a->1c); affects

FOV=4 only

- added

S-Link CRC in DDU trail word for CMS Common Data Format

- reassign

DDU Status Bit 5 as Trigger_CRC_Error flag (FOV=4 only?)

- OLD Production DDU Format: Input from DMB, Output from DDU

- FOV==5,

used Sept. 2005 - Aug. 2007 for Slice test & MTCC; small red DDU

- format

change summary:

- modified

DMB Second Header word 2a and all DMB Trail words

- modified

CFEB word 99 of each time sample

- modified

DDU Header 2, Header 3, Trail-1

- reassign

DDU Status Bits 22, 28-31

- set

SourceID to decimal 760 (2F8h) for TF S-Link, was D62h

- Previous Production DDU Format: Input from DMB, Output from DDU

- FOV==6,

used Sept. 2007 through mid-2014; small red DDU

- format

change summary:

- added

unique ALCT & TMB Header words

- modified

ALCT & TMB Trailer words

- modified

CFEB sample word 100

- Current production DDU Format (for post LS1): Input from DMB, Output from DDU

- FOV==7,

begin use mid-2014 for post-LS1; small red DDU

- format

change summary:

- Accomodates the new uniform DMB & ODMB data format for handling up to 7 CFEBs

- The DDU now sends the real CMS Source ID in the first Header word

Historical

Hardware Info: the DDU Prototypes

The third DDU prototype design (final pre-production prototype, small & green) is a 220 mm 9U VME64x board. Except for the color, it is essentially the same as the Production DDU; there are minor changes such as clock distribution and ground connections. The parts and Data Format used are the same as for the Production DDU. It can be distinguished from the 2nd prototype by noting the presence of 8 FIFOs.

The second DDU prototype design (small & green) is a 220 mm 9U VME64x board. The major difference from later DDUs is that this design used 4 large external DDR FIFOs (IDT 72T40118) that have a manufacturing flaw which causes a small-but-measurable rate of bit errors. The data is transmitted with the Prototype DDU Data Format. It can be distinguished from other prototypes by noting the presence of only 4 FIFOs.

The first DDU prototype (big & red) is a 400 mm 9U VME64x board; firmware updates were made in October 2004 such that it functions basically the same as the 2nd prototype. The only significant difference for the user is that the 1st DDU Prototype Data Format. removes all DDU Code 9 words from the DMB data stream; these words are retained by all later prototypes. Prior to October 2004 the big red DDUs used the Early Prototype Data Format, which is still in use for the Partial DDU at UCLA. This data format is not compatible with the latest CMS Common Data Format. There are some parts that are unique to the first prototype: the data from each fiber gets deserialized (TI TLK2501) and stored in a high speed FIFO receive buffer (IDT 72V7270L10); data is read out and monitored by the DDU Control FPGA (Xilinx XCV600E-FG676-7C).

![[ddu_production.jpg]](http://www.physics.ohio-state.edu/~cms/ddu/ddu_production.jpg)